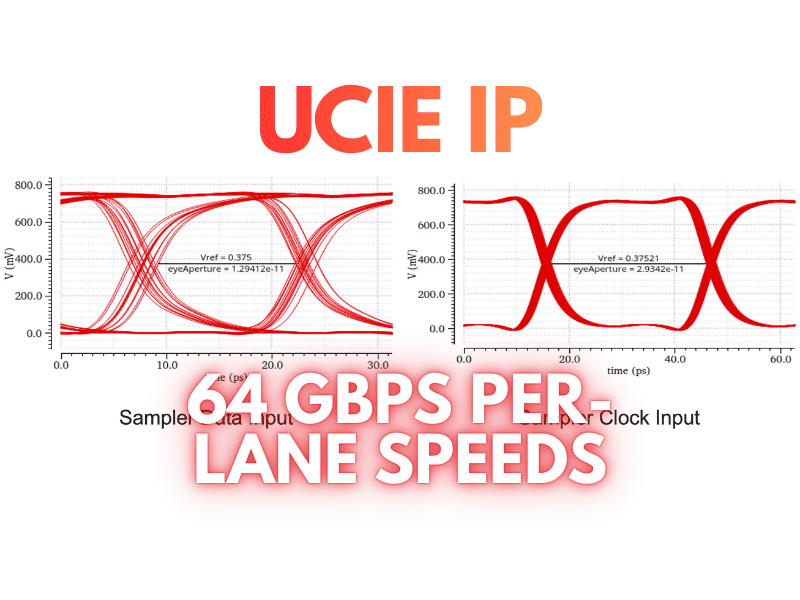

Cadence已开发出第三代通用芯片互连快递(UCIe)IP解决方案,支持台积电N3P流程中每通道最高64 Gbps的数据速率。这一发展反映了基于芯片组架构的持续势头,设计师们推动更高带宽和更紧密的集成,尤其是在先进节点上。

此次更新具有相关性,因为UCIe IP正日益影响工程师如何处理多芯片集成,尤其是在AI加速器、高性能计算和数据中心平台中,带宽密度和能效正成为系统层面的限制。

UCIe IP 目标是高级节点的更高带宽

据Cadence称,流片的UCIe IP符合UCIe规范,旨在支持尖端工艺技术下的可扩展的芯片对芯片互连。迁移到台积电的N3P节点有望实现比早期实现更高的每瓦性能,尽管最终的系统级提升将取决于封装、集成选择和工作负载配置文件。

公司将该解决方案定位为更广泛推动解决随着设计转向3nm级节点而出现的功耗、性能和面积权衡的一部分。高速芯片对芯片连接在此背景下变得越来越关键,尤其是在单体扩展被异构集成策略取代的情况下。

Cadence指出,该IP支持多种协议,包括AXI、CXS、CHI-C2C、PCIe和CXL,这些协议可简化集成到多种基于芯片组的系统。这种灵活性对于跨混合供应商生态系统或针对不同平台重用的欧洲系统设计师可能具有相关意义。

人工智能和高性能计算系统的芯片组连接

UCIe IP每通道64 Gbps,定位支持芯片组间高总带宽,这是AI和高性能计算工作负载的关键需求。Cadence报告的带宽密度数据因封装方式而异,表明先进封装技术仍然是实现高速互连IP全部潜力的关键因素。

该解决方案还包括纠错、车道空间和诊断支持等功能,旨在提升启动和运行过程中的稳健性。Cadence指出,自校准能力可能减少系统初始化时对固件干预的需求,从而可能缩短开发周期。

“自2018年首次录音出厂以来,Cadence一直走在全线接口解决方案的前沿。2022年转向UCIe,过去两年我们广泛演示了第一代和第二代UCIe解决方案的硅质证明。“Cadence硅解决方案集团市场副总裁Arif Khan说,“鉴于AI和高性能计算应用对吞吐量和效率的巨大需求,我们自豪地推出了第三代UCIe IP——实现64G的速度。”

<!-- 非定向300*250按钮 17/09 wenjing begin --> <!-- 非定向300*250按钮 end -->

</div>