安森美(onsemi)的碳化硅(SiC)系列产品“EliteSiC”可以为能源基础设施和工业驱动应用提供高能效、高可靠性的解决方案。1700 V EliteSiC MOSFET具有更高的击穿电压(BV),最大Vgs范围为-15 V/25 V,适用于快速开关应用,其栅极电荷(Qg)在1200 V、40 A条件下仅为200 nC,远低于同类竞争产品。两款肖特基二极管在1700 V额定击穿电压下,具有出色的反向漏电流性能,最大反向电流(IR)在25°C时为40 µA,175°C时为100 µA,显著优于竞争对手。

新的1700 V EliteSiC器件针对可再生能源应用中向更高电压发展的趋势,如太阳能系统从1100 V向1500 V直流母线升级,提供了更高的击穿电压(BV)值,满足快速开关和高功率应用的需求。此外,安森美还关注热插拔控制器的设计需求,特别是在高电压(400 V至800 V)系统中,如数据中心用于AI计算等场景,需要合适的解决方案来实现安全的热插拔功能,避免高涌入电流对系统造成损坏。

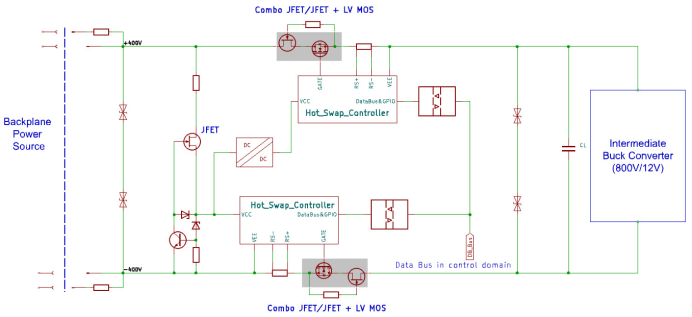

图

1.

简化框图

图

1.

简化框图本应用说明将重点介绍onsemi EliteSiC组合JFET用于热插拔应用,包括优势、工作模式描述、设计实践和测试结果等。

1. 产品介绍

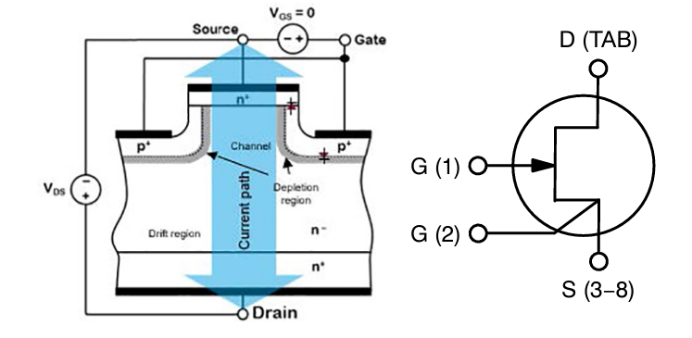

EliteSiC JFET 基于设备JFET是最简单的场效应晶体管(FET)设备,具有直接的漏极到源极电流路径。这种简单的结构提供了最低的导通电阻,并且没有影响可靠性的栅极电荷陷阱或表面电流。图2显示了JFET的结构。JFET是一个常开设备,这意味着在没有施加负栅极偏置的情况下,设备是开启的。要切换或保持其关闭,需要施加负电压(低于其阈值电压)。

图2. JFET结构(左:结构,右:符号)

图2. JFET结构(左:结构,右:符号)onsemi提供两种基于SiC JFET的常关设备类型:

• CJFET(级联JFET),碳化硅(SiC)JFET

• Combo JFET,碳化硅(SiC)组合JFET

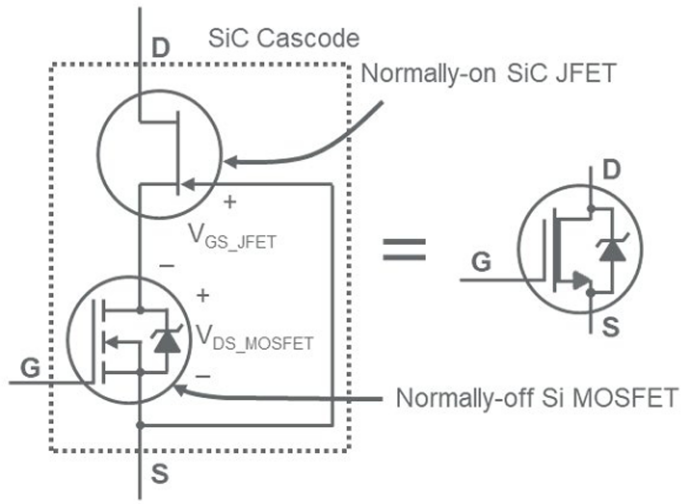

CJFET利用低电压MOSFET和JFET的级联配置。MOSFET作为JFET源的开关,而JFET的栅极连接到MOSFET的源。该配置的电路图和符号可以在图3中找到。

图3. CJFET结构

图3. CJFET结构当低电压MOSFET的栅源电压(VGS)高于其阈值电压时,MOSFET开启。当JFET源连接到MOSFET漏极且其栅极连接到MOSFET源时,由于VGS_JFET超过其阈值,JFET被开启。相反,当MOSFET的VGS较低(且处于关闭状态)时,施加在CJFET上的外部电压将增加MOSFET的VDS,直到超过JFET的阈值电压,从而关闭JFET并使CJFET能够阻挡高电压。CJFET主要用于高频开关模式应用。

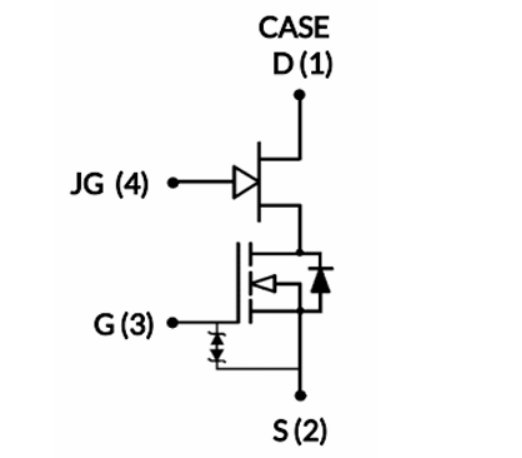

Combo JFET与CJFET的级联配置相似,但有一个关键区别,即JFET的栅极可以外部访问。对JFET栅极的外部访问提供了几个优点,包括:• 通过过驱动降低导通电阻• 增加线性模式控制的稳定性• 可调的开关速度以减少过冲并便于并联• 监测结温的能力

对于热插拔等电路保护应用,线性模式稳定性和可调开关速度至关重要。这就是为什么推荐Combo JFET用于热插拔应用。图4显示了Combo JFET的符号。

图4. Combo JFET符号

图4. Combo JFET符号详细信息请参见UM70113 – JFET和Combo JFET用户指南

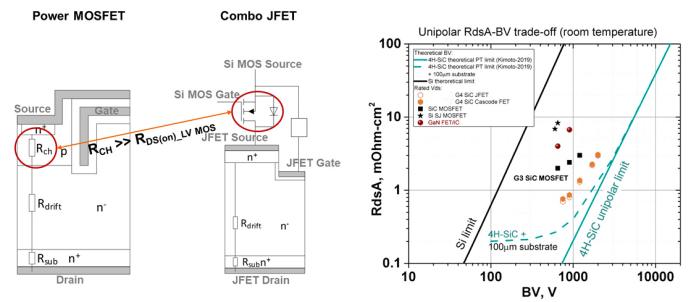

Combo JFET在热插拔应用中的优点:低导通电阻Rds(on)在正常操作期间最小化电压降和功耗,当功率FET完全开启时。基于JFET的设备具有比MOSFET设备更低的Rsp,下面的图显示了不同技术之间的原因和测试的RdsA。

图5. JFET和MOSFET之间的结构和RdsA比较

图5. JFET和MOSFET之间的结构和RdsA比较2. 强安全操作区域 (SOA)

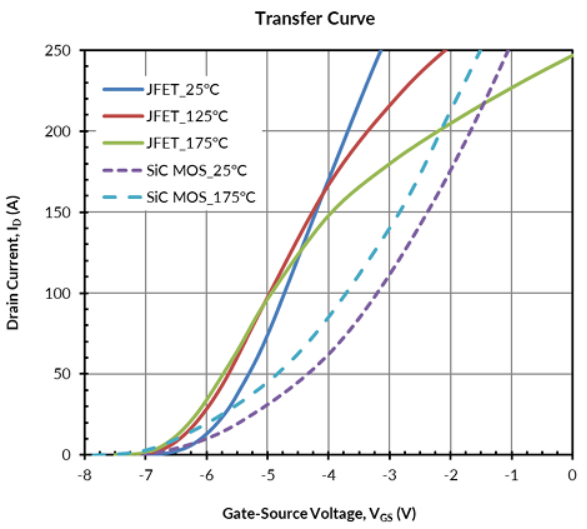

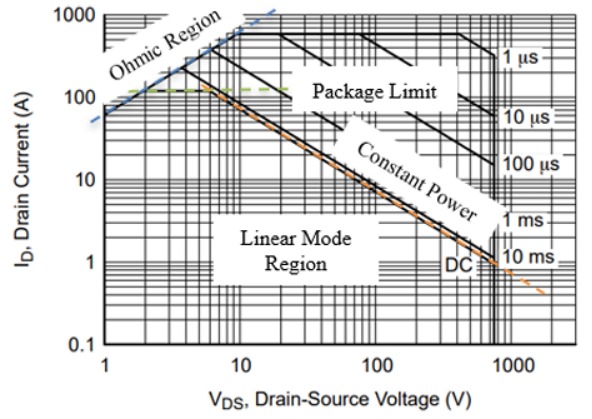

在热插拔过程中,功率FET两端的电压最初完全是直流链接总线电压,并在直流链接电容器完全充电时降至零电压。为了保持功率FET的结温在规格范围内,充电电流通常相对于其正常工作电流非常低。这种操作可能会导致现代功率FET的热不稳定性问题。热稳定性由转移曲线上正温度系数区域的大小来定义。下图显示了1200 V/7 m JFET和MOSFET的转移曲线示例。明显可以看出,SiC JFET的PTC区域相对小于SiC MOSFET。

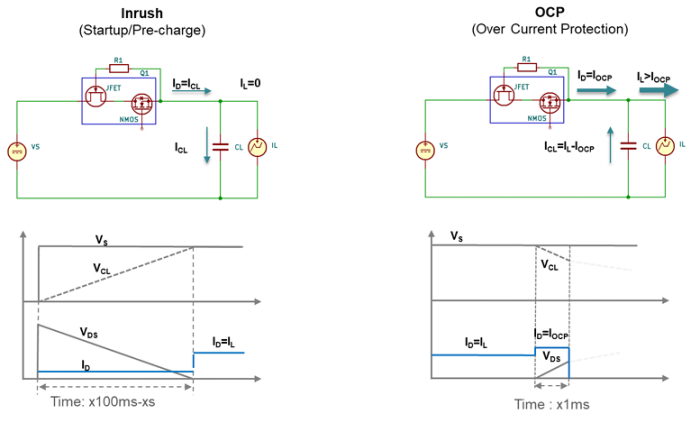

电流限制:热插拔功率FET需要限制电流以确保系统和自身的安全。热插拔应用有两种电流限制场景:启动(直流链接电容器预充电)和过流保护(OCP)。图7显示了启动和OCP电流限制的工作条件。

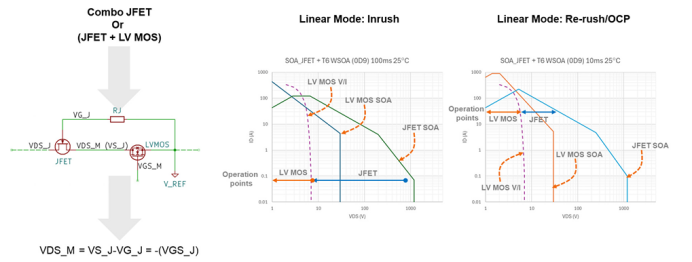

Combo JFETs 可以在电流限制(线性模式)稳定性下工作,它们已与热插拔控制器在 400 V 和 800 V 系统中进行了测试。图 8 说明了 Combo JFETs 在启动和过流保护(OCP)期间的线性模式操作的工作原理。

门驱动电压兼容性:大多数热插拔控制器的门偏置电压在 10 V 到 12 V 之间,功率半导体的门驱动电压需要与热插拔控制器兼容。由于低电压硅 MOSFET 门输入,Combo JFET 与所有热插拔控制器具有通用的门兼容性。图 9 显示 10 V − 15 V 的门电压可以使 Combo JFET 完全导通。

3.热插拔控制方法

热插拔控制器感测电流输出和输入/输出电压以进行控制,请参考控制器以获取详细信息。在本应用说明中,我们将讨论涌入控制方法,因为涌入或启动阶段对功率器件的压力更大。限制涌入电流有两种典型方法,一种是 dv/dt 控制/模式,另一种是主动电流限制。

带外部 Cgd 的 dv/dt 控制

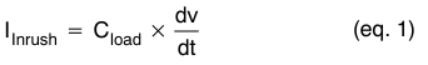

恒定输出电压斜率(dv/dt)可以控制涌入电流值,限制的电流水平由以下公式定义:

功率 FET 的 dv/dt 在门到源电压处于阈值水平时由恒定的门驱动电流控制。

这恒定栅极驱动电流控制功率FET dv/dt 通过 Cgd,遵循:

基于 (公式 1) 和 (公式 2) 突入电流定义为公式 3。

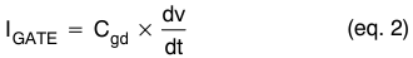

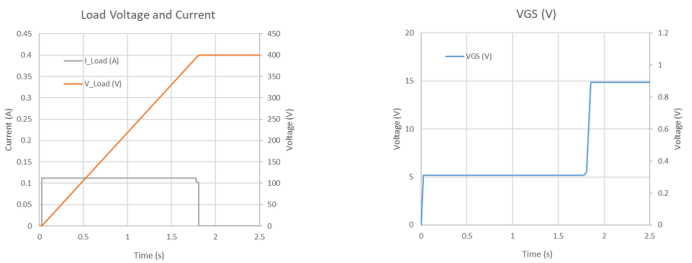

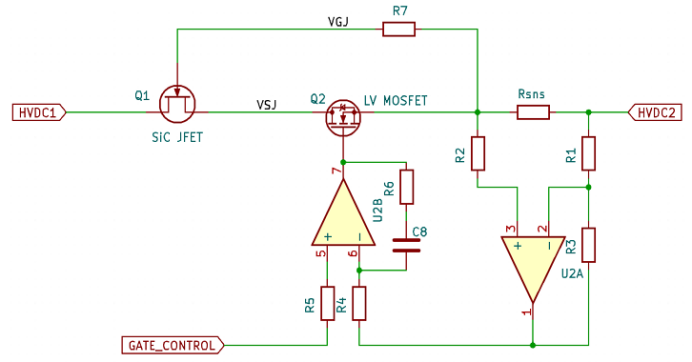

热插拔控制器在 5 µA – 20 µA 水平提供恒定栅极驱动电流。外部 Cgd 可能是必要的,以保持突入电流在不同负载电容水平下处于功率 FET SOA 内。离散解决方案如图 10 所示,模拟结果如图 11 所示。此处演示了级联结构,Q1 是 SiC JFET,Q2 是低压 MOSFET。onsemi 提供单独的 JFET 和 LV MOSFET,或组合 JFET,将两个芯片封装在一个包中。

图 10. 离散 dv/dt 控制原理图

图 10. 离散 dv/dt 控制原理图 图 11. dv/dt 控制仿真结果

图 11. dv/dt 控制仿真结果连续电流闭环模式:控制器感测负载电流此感测电流反馈到恒定电流控制环路,并与电流设定值进行比较。感测电流与设定电流值之间的差异被放大以驱动功率 FET 栅极。在 JFET 的漏极和 LV MOSFET 的栅极之间仍然需要一定水平的外部 Cgd 以稳定控制。离散设计如图 12 所示,以展示电流闭环控制的原理。

图12. 电流闭环控制框图

图12. 电流闭环控制框图不连续电流闭环模式:电流闭环控制需要足够的电流感应分辨率以准确控制电流,因此存在最小可控电流水平。如果最小可控电流水平高于SOA能力,则可以使用不连续模式(升压模式)方法。不连续模式意味着电流处于最小可控水平,具有一定的脉冲长度(在SOA范围内),并在两个主动电流脉冲之间有一定的冷却时间。该方法平衡了电流控制分辨率和SOA限制。

4.设计实践

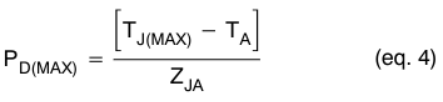

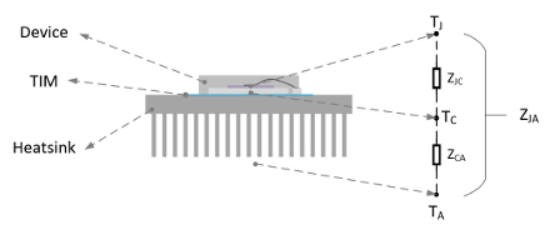

热能力:保持结温在规范范围内的最大允许功率损耗由热阻抗和环境温度决定(公式4)。

公式4中的ZJA是从器件结到环境的阻抗。热堆栈如图13所示。从结到外壳的热阻抗(ZJC)被表征并在数据表中以不同脉冲持续时间的曲线显示。从外壳到环境的热阻抗(ZCA)应由应用设计师进行表征。

图13. 热阻抗

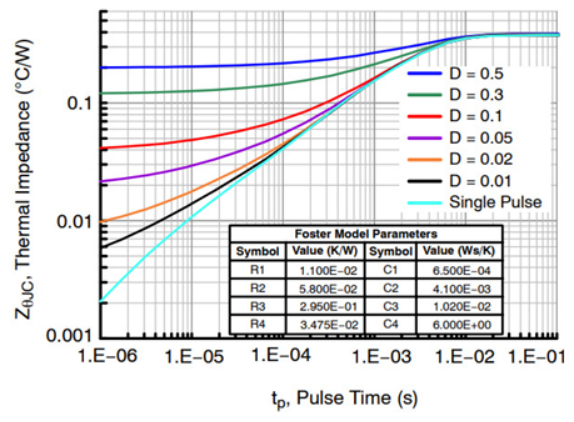

图13. 热阻抗RC热模型(Foster或Cauer)是功率FET热阻抗的等效表示,以支持在SPICE模拟器中使用的计算或仿真。Foster模型适用于SiC组合JFET。图14显示了热瞬态曲线和Foster RC网络。

图14. UG4SC075009K4S热阻抗

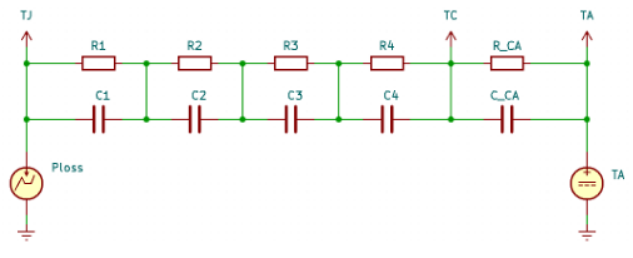

图14. UG4SC075009K4S热阻抗图15指示了包括外壳到环境的热模型的结温仿真。Ploss是模拟器中的电流源,表示功率FET的瞬时功率损耗,TA是表示环境温度的电压源。

图15. 热模型(Foster)

图15. 热模型(Foster)案例到环境热阻和电容影响结点温度,进行SPICE仿真以显示基于UG4SC075009K4S和表1中的条件。

表1

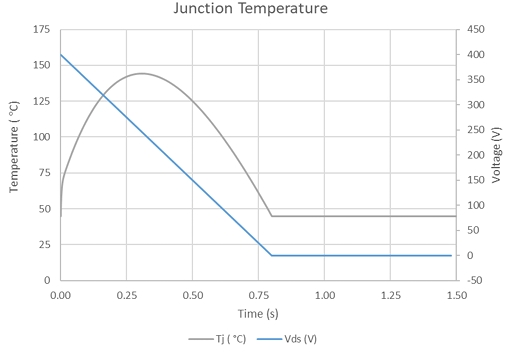

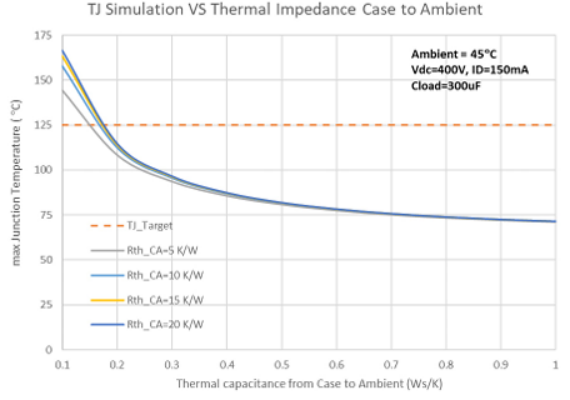

表1仿真(图16)显示在特定的案例到环境热阻抗(Rth_CA = 5 K/W和Cth_CA = 0.1 Ws/K)下,基于UG4SC075009K4S的启动电流限制操作期间的结点温度。

图16. 结点温度仿真结果

图16. 结点温度仿真结果图17显示了不同案例到环境热阻和电容的仿真结果。从这些仿真结果来看,当热电容足够高(>0.2 Ws/K)时,热阻的容忍度很高(从5 K/W到20 K/W)在启动期间。

图17. 不同案例到环境热阻抗的Tj仿真结果

图17. 不同案例到环境热阻抗的Tj仿真结果散热器的热阻由给定设计的气流决定,热电容可以用(公式5)计算:

热界面材料(TIM)被视为Z CA的一部分,实际热阻抗应通过测试测量。

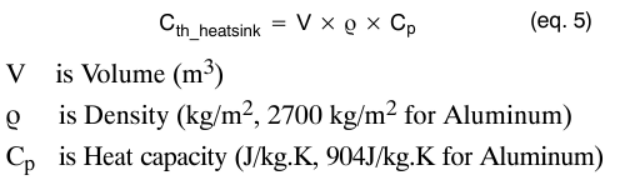

热稳定性:功率FET的SOA曲线可能显示不同脉冲宽度和外壳温度下的理想化漏源电压(VDS)和漏电流(ID)曲线。

图18. SOA曲线 − 恒定功率线

图18. SOA曲线 − 恒定功率线当功率FET导通时,基本上有两种不同的操作模式:

• 欧姆区:VDS 值遵循ID x Rds(on)的规则

• 线性模式区:VDS 值与ID 无关,VDS 由外部电路决定,ID 由VGS 控制(ID = k(VGS − VTH ) ² )

与相同的电流水平,当功率器件在线性模式下工作时,其功率损耗显著高于在欧姆模式下工作时。用于浪涌电流限制的功率FET将相对较长时间进入线性模式,与其热瞬态时间相比。这就是为什么预充电电流通常较小,必须根据环境和热能力在安全工作区(SOA)内,特别是之前讨论的热电容。然而,实际部件在高VDS区域可能表现出不同的行为,实际SOA上的电流与恒定功率线相比更小。这种现象被称为“Spirito效应”,是由于局部热点的形成。功率FET的转移曲线显示了在给定结温和漏源电压(VDS)下,漏电流(ID)作为栅源电压(VGS)的函数。图18显示了onsemi第四代SiC JFET的典型转移曲线。在不同结温下,两条曲线之间存在交叉点。在这个点上,当结温变化时,漏电流不会改变,这意味着温度系数为零(ZTC)。在这个点以下,由于结温升高,漏电流变得更高,可能会形成热点。芯片上的更热区域集中更多电流,导致进一步加热,并可能因局部区域的热失控而失效。AND90317 – SiC JFET在主动模式应用中显示了基于转移曲线和热瞬态的稳定性分析方法。

图19. SiC JFET转移曲线

图19. SiC JFET转移曲线当功率损耗增加超过功率可以热散失的能力时,就会发生热失控。

∂ P_loss(t) / ∂ T_J(t) ≥ ∂ P(t) / ∂ T_J(t) (公式6)

其中 P_loss(t) = I_D(t) * V_DS(t) 和 ∂ T_J(t) = ∂ P(t) / Z(t),热稳定性的条件可以表示为:

∂ I_D(t) / ∂ T_J(t) ≥ 1 / Z(t) * V_DS(t) (公式7)

对于热插拔应用,所有参数都会变化,包括不同的结温、时间或电压。因此,通过测试实际设计进行验证比基于公式6和7的理论分析更可靠。

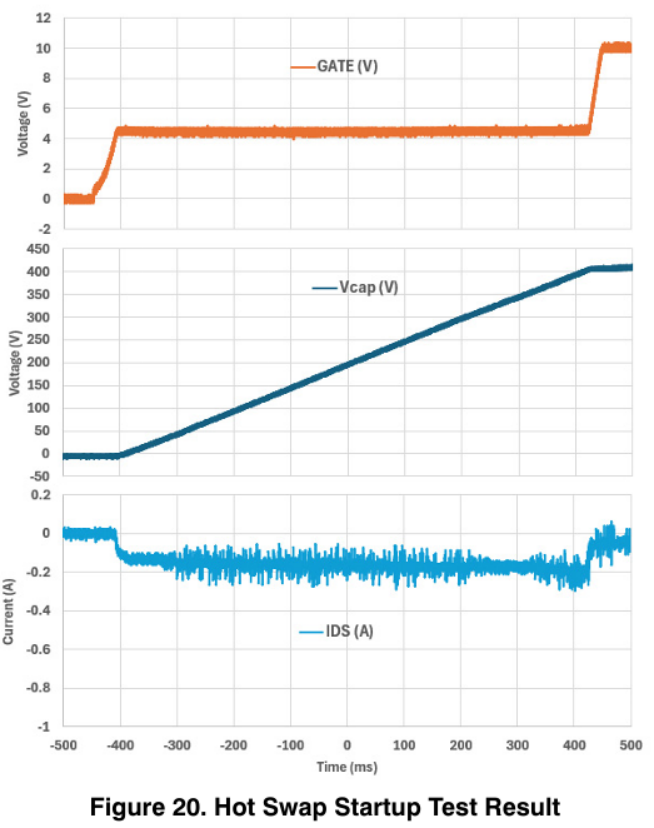

测试结果

组合JFET(UG4SC075011K4S)在热插拔控制器下测试,用于将330μF电容器充电至400V,充电电流为160mA,完全充电的时间为800毫秒。

图20. 热插拔启动测试结果

图20. 热插拔启动测试结果 <!-- 非定向300*250按钮 17/09 wenjing begin --> <!-- 非定向300*250按钮 end -->

</div>