碳化硅(SiC)凭借其优异的材料特性,在服务器、工业电源等关键领域掀起技术变革浪潮。本教程聚焦 SiC 尤其是 SiC JFET 系列器件,从碳化硅如何重构电源设计逻辑出发,剖析其在工业与服务器电源场景的应用价值。

我们已经介绍了

碳化硅如何革新电源设计、工业与服务器电源。

三种替代 Si 和 SiC MOSFET的方案。

本文为第三篇,将介绍SiC Cascode JFET的动态特性、SiC Combo JFET的应用灵活性。

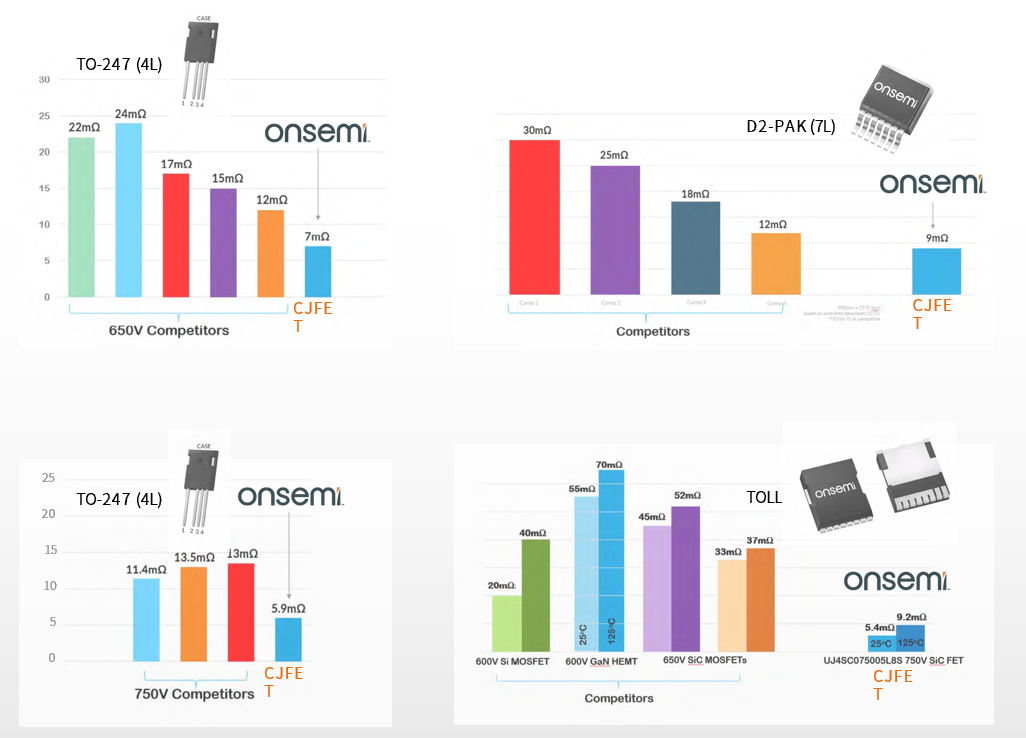

对于当前市场上任意给定的半导体封装,CJFET 始终能提供最低的导通电阻 RDS(on)。您无需并联多个器件来提升性能,从而节省宝贵的 PCB 空间。

安森美(onsemi)采用 TOLL 封装的 750 V UJ4SC075005L8S CJFET 在 25°C 时的 RDS(on) 仅为 5.4 mΩ。相比之下,竞品器件即使额定电压仅达 600 V 或 650 V,其 RDS(on)仍可能高达该值的十倍之多。

正得益于这一显著的导通电阻优势,安森美的 EliteSiC CJFET 如今在成本与性能两方面,均能有力地与硅基超结 MOSFET(Superjunction MOSFET)展开有力竞争。

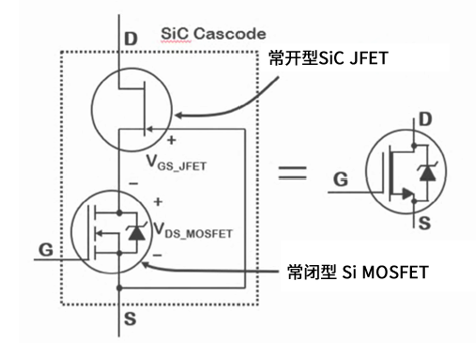

SiC CJFET的工作机制如下:在器件导通阶段,向低压硅 MOSFET(LVMOS)的栅极施加 12 V 至 15 V 的正向驱动电压,使其沟道导通。在此期间,阻抗很低,其漏源电压 VDS 迅速降至 0V。而恰好 0V 即为 SiC JFET 的导通电压,因此器件也随之导通。

在关断阶段,将 LVMOS 电压置为 0V。漏极偏置电压会通过 SiC JFET 传递,导致 LVMOS 的漏源电压 VDS 升高。这种电压反转会充当 JFET 的栅极驱动信号,当 LVMOS 的 VDS 超过 SiC JFET 的阈值电压时,JFET 的导电沟道被夹断(pinch-off),从而阻断系统中剩余的全部高压。

除了导通电阻和导通损耗的优势外,

除了导通电阻和导通损耗的优势外,